Vertikale Chipkontaktierungen durch den Halbleiter (Through Silicon Vias, TSV) stellen eine zukünftige Schlüsseltechnologie für den Aufbau komplexer und hochleistungsfähiger 3D-integrierter Systeme der Nanoelektronik dar. Für die entwicklungsbegleitende Prozesskontrolle sowie Sicherung einer hohen Fertigungsqualität und Zuverlässigkeit von TSV-Kontakten werden neue und innovative Diagnostiktechniken benötigt.

Fehleranalytik für Through Silicon Vias

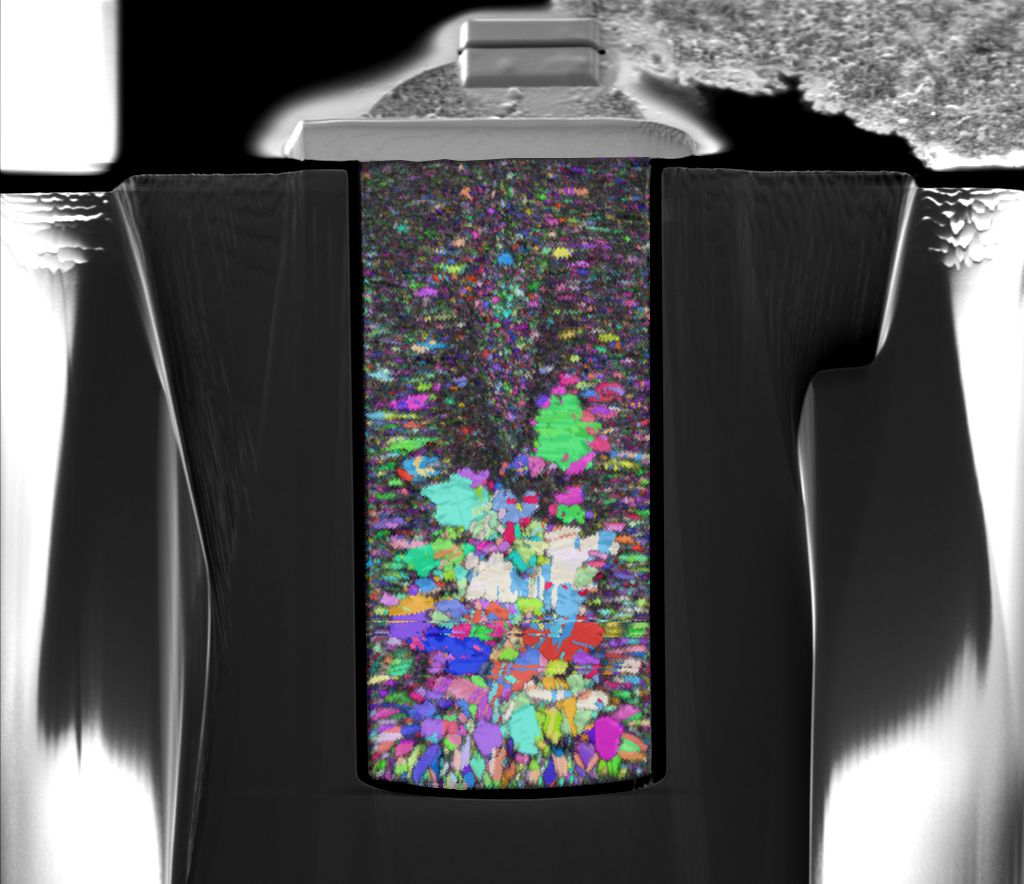

Bei der Herstellung von TSVs werden Durchführungen in den Halbleiter geätzt, diese am Rand mit einer dünnen Siliziumoxidschicht isoliert, danach eine Diffusionsbarriere und weiterhin eine Keimschicht für die folgende galvanische Kupfer-Füllung abgeschieden. Ein dabei auftretender Defektmechanismus ist die Hohlraumbildung innerhalb des Metalls. Für eine zerstörungsfreie TSV-Inspektion wurde ein Detektionsverfahren basierend auf der akustischen Ghz-Mikroskopie entwickelt. Mit ihm können hohlraumartige Defekte in μm-großen TSV-Geometrien nachgewiesen werden. Ein weiteres TSV-Fehlerrisiko stellen Schwachstellen in der elektrischen Randisolierung dar. Mit einer Kombination aus Lock-in-Thermographie und Stromabbildung im Rasterelektronenmikroskop war es möglich, derartige leckstromverursachende Defekte innerhalb der dreidimensionalen Lochgeometrie exakt zu lokalisieren. Für die großflächige Inspektion solcher Schwachstellen wurde ein selektives nasschemisches Rückätzverfahren erfolgreich erprobt. So können TSV-Kontakte freigelegt und anschließend hochauflösend inspiziert werden. Als weitere neue Präparationstechnik wurde ein Laser-Tool zur μm-präzisen und zeiteffizienten Herstellung von Zielquerschnitten für die elektronenoptische Analyse entwickelt. Mittels Laser-Ablation werden Querschnitte durch den gesamten TSV vorpräpariert und anschließend mittels Hocheffizienz-Plasma-FIB poliert. In Kombination beider Techniken konnten die Präparationszeit signifikant reduziert und damit komplette TSV-Strukturen für die Analyse zugänglich gemacht werden. Damit wird auch eine Untersuchung des Korngefüges der Kupfer-Füllung mittels Rückstreuelektronenbeugungs-Analyse (EBSD) ermöglicht, die für die Bewertung von Zuverlässigkeit und Einsatzverhalten der TSV wesentlich ist.

Bestimmung lokaler Eigenspannungen

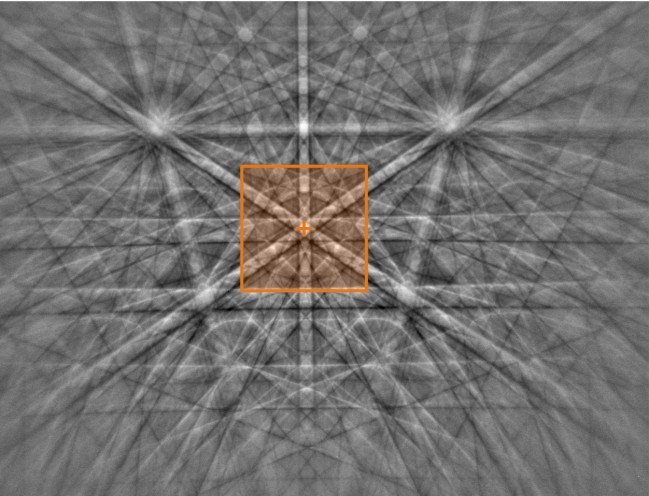

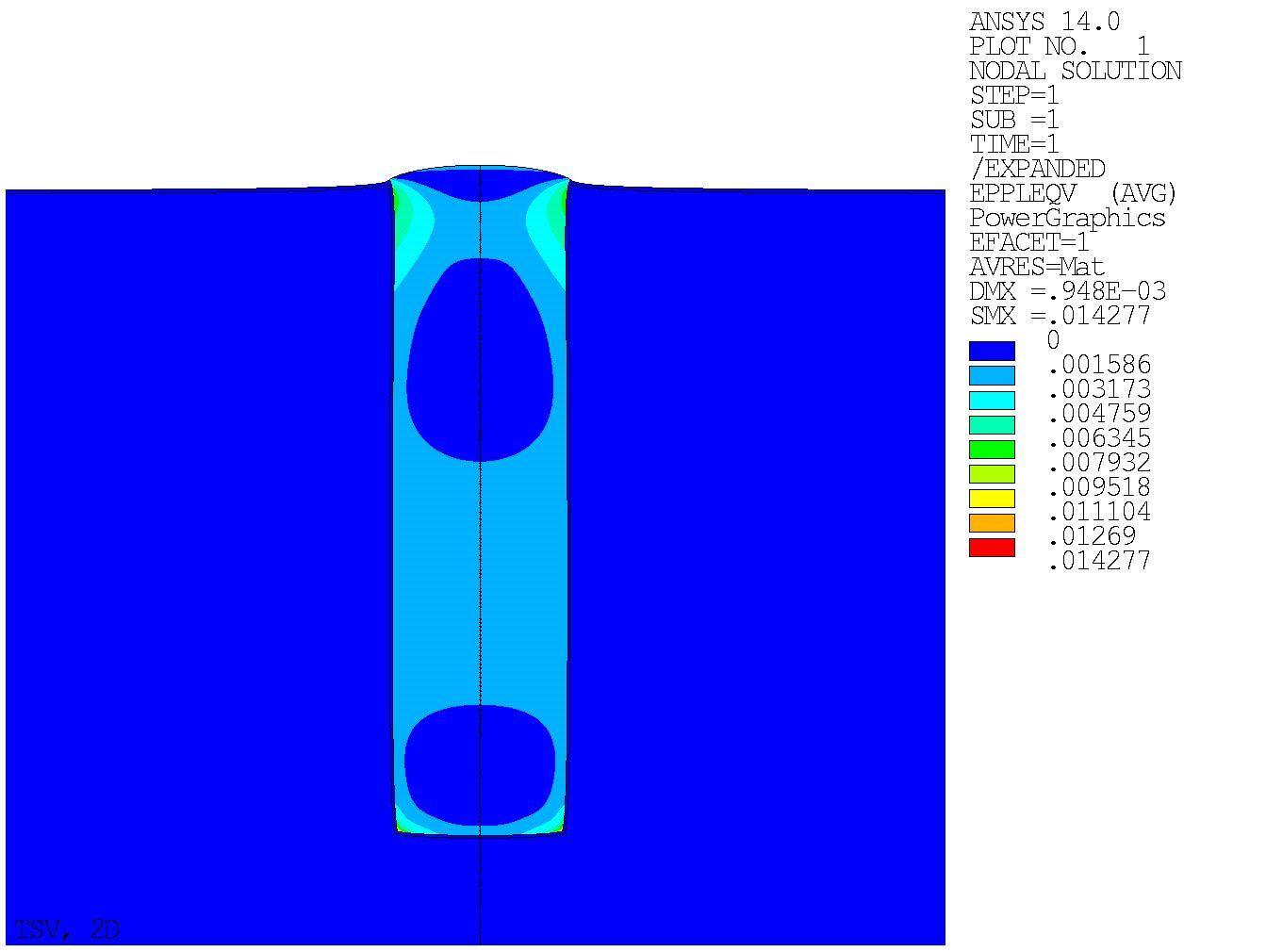

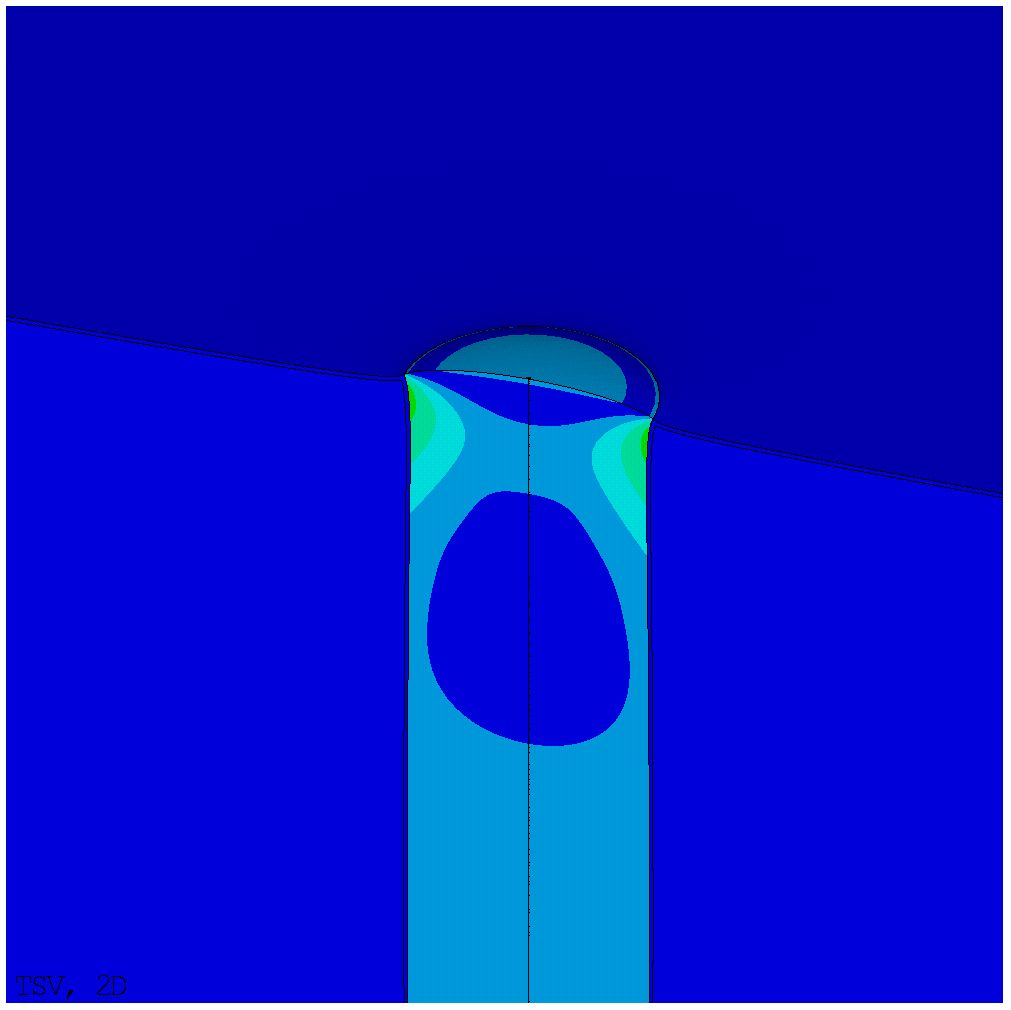

Aufgrund der thermomechanischen Fehlanpassung zwischen Kupfer und Silizium entstehen in TSV-Strukturen hohe lokale Eigenspannungen, die ein Herausdrücken des Metalls und Rissdefekte im Chip verursachen können. Für eine Risikoabschätzung und vergleichende Bewertung von Prozessvarianten wurde die Verteilung von Eigenspannungen im TSV mittels Finite-Elemente-Simulation analysiert. Für die Messung der lokalen Eigenspannungsverteilung ist parallel dazu ein Verfahren zur lokalen Messung der Gitterverzerrung im Silizium basier end auf Elektronenrückstreubeugung (EBSD) weiterentwickelt worden. Mit einem neuen Bildanalysealgorithmus können Kikuchi-Beugungsbilder von Referenz- und Messposition präzise verglichen und daraus die dreidimensionale Gitterverzerrung bestimmt werden. Aktuell wird diese Technik für die Messung der Eigenspannungsverteilung am TSV-Kontakt evaluiert, um die FEM-Modelle zu verifizieren.

Ausblick

In Zusammenarbeit mit dem Fraunhofer IZM-ASSID, mit RTI International (USA) sowie mit Firmenpartnern unterstützen die neu entwickelten Analyseverfahren die technologische Entwicklung von qualitätsgerechten TSV-Kontaktierungen der mikroelektronischen 3D-Integration. Die innovativen Diagnostikkompetenzen des Geschäftsfeldes werden zukünftig auch für die Analyse von Zuverlässigkeitsrisiken und des Einsatzverhaltens von 3D-integrierten Bauelementen der Nanoelektronik für verschiedene Anwendungsfelder eingesetzt werden.